# Laboratorio di Segnali e Sistemi - Esercitazione -7 - Costruzione di un ADC

last update : 070117

## Argomenti dell'esercitazione:

- Costruzione di un ADC:

- Contatore

- DAC a pesiera a 4 bit

- Comparatore d'ingresso

- Adattore di livello logico

In appendice riportate alcuni grafici/screenshot relativi all'esperienza 6

Il clock è fornito dal generatore (onda quadra tra 0 e 5 V; potete variare la frequenza)

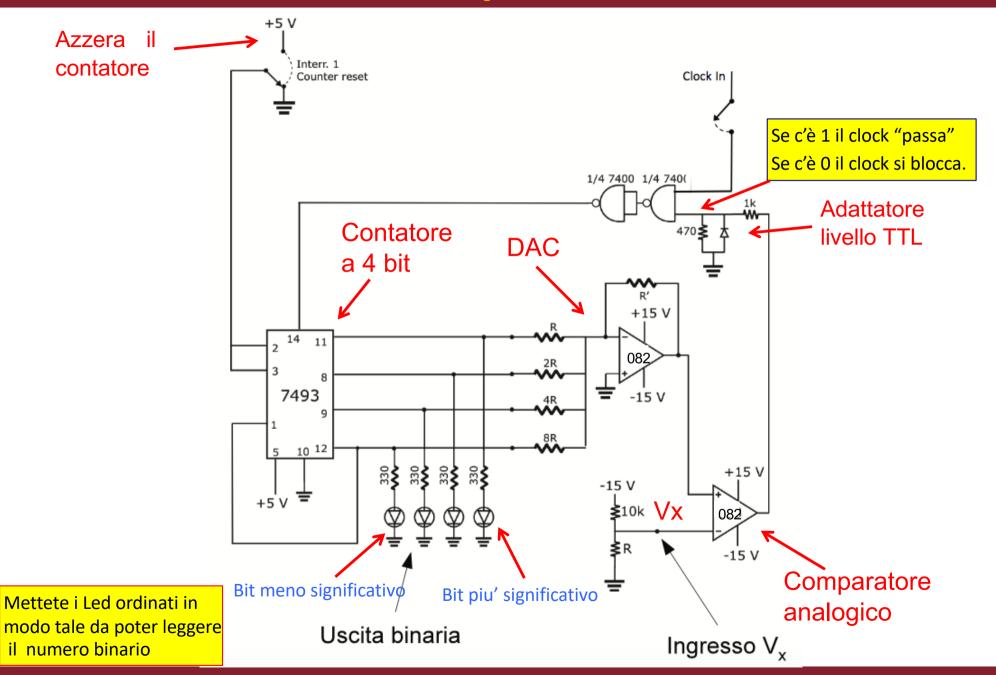

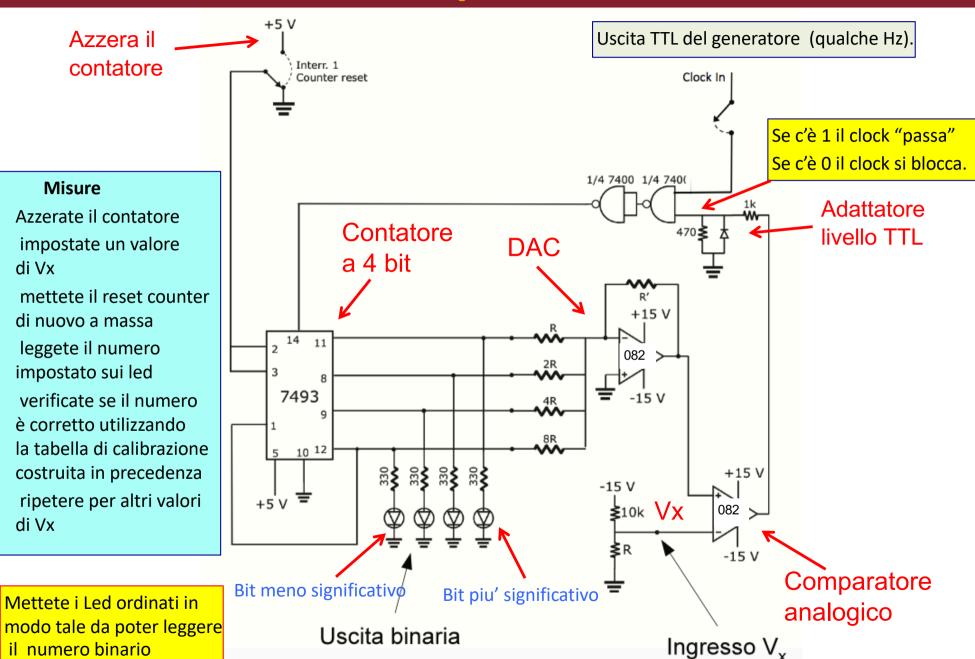

## Costruzione dell'ADC

- $\triangleright$  Questa esercitazione è dedicata alla costruzione di un convertitore analogico-digitale (ADC) a 4 bit, ovvero un dispositivo che riceve in ingresso una tensione  $V_x$  e fornisce in uscita un numero binario a 4 bit ad essa proporzionale

- ➤ Lo schema complessivo è riportato nella slide successiva in cui si distinguono i vari blocchi funzionali:

- Contatore

- Comparatore d'ingresso

- Convertitore digitale-analogico (DAC) a pesiera

- Adattore di livello logico

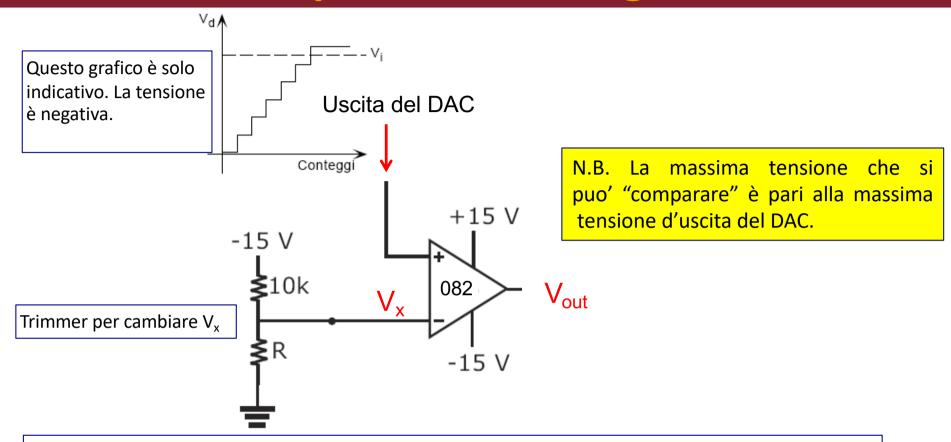

- La tensione da convertire,  $V_x$ , deve essere **negativa** e compresa tra **0 e -5 V**; può essere ottenuta con un partitore a partire dai -15 V dell'alimentazione (in alternativa al partitore si può usare un trimmer).

- ➤ L'uscita del comparatore (15 V / -15 V) viene riportata ai livelli logici standard TTL tramite il blocco "adattore di livello logico".

- Conviene realizzare il circuito costruendo un blocco per volta e verificandone man mano il funzionamento. È importante che il montaggio sia effettuato con cura e con un buon ordine.

Il trimmer è un potenziometro

## Circuito completo dell'ADC

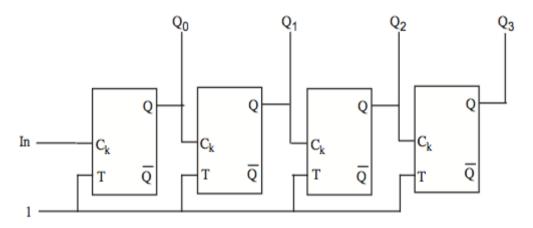

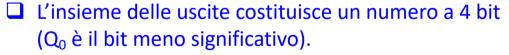

## **Contatore** asincrono

- ☐ Si può costruire un contatore binario utilizzando dei flip-flop di tipo T master-slave.

- Tutti gli ingressi vengono posti a 1; gli impulsi da contare entrano nel clock del primo stadio, mentre ogni uscita fornisce il clock allo stadio successivo. Poiché i flip-flop sono master-slave, ogni uscita commuta sul fronte di discesa del clock ricevuto all'ingresso,

come si vede in figura, dove abbiamo supposto che inizialmente tutti i flip-flop siano a zero:

Si può anche notare come le frequenze di commutazione vengano dimezzate man mano, quindi questo circuito può anche essere usato come un divisore di frequenza, per potenze di due.

| Numero di impulsi | $Q_3$ | $Q_2$ | $Q_1$ | $Q_0$ |

|-------------------|-------|-------|-------|-------|

| 0                 | 0     | 0     | 0     | 0     |

| 1                 | 0     | 0     | 0     | 1     |

| 2                 | 0     | 0     | 1     | 0     |

| 3                 | 0     | 0     | 1     | 1     |

| 4                 | 0     | 1     | 0     | 0     |

| 5                 | 0     | 1     | 0     | 1     |

| 6                 | 0     | 1     | 1     | 0     |

| 7                 | 0     | 1     | 1     | 1     |

| 8                 | 1     | 0     | 0     | 1     |

|                   |       |       |       |       |

| 15                | 1     | 1     | 1     | 1     |

| 16                | 0     | 0     | 0     | 0     |

### Contatore a 4 bit

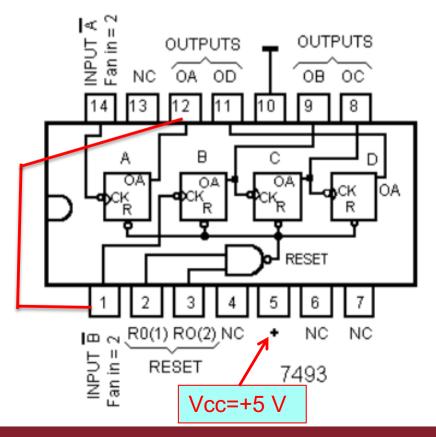

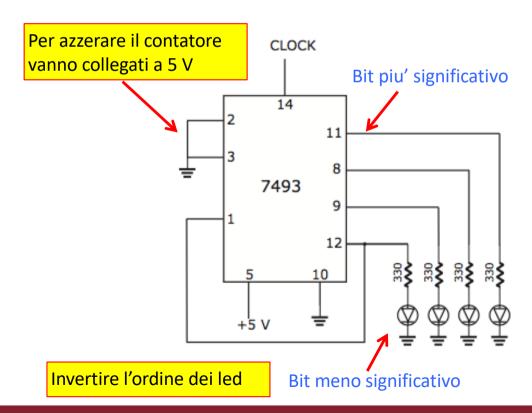

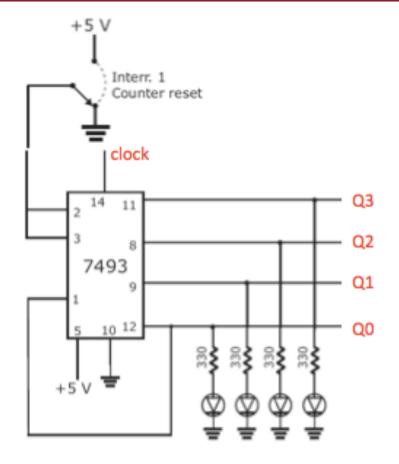

Dobbiamo anzitutto costruire il contatore che utilizzeremo per pilotare il DAC. Possiamo utilizzare l'integrato 7493 (Fig. 6.1) montato come suggerito nella Fig.6.2. Per verificarne il funzionamento inviare all'ingresso di Clock un'onda quadra con ampiezza tra 0 e 5V e frequenza di circa 1 Hz. Si dovrebbe essere in grado di visualizzare la sequenza di accensione dei LED's verificandone la correttezza.

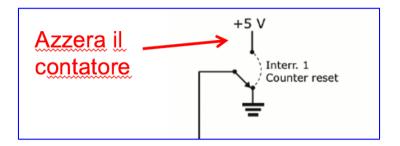

Si noti che, nel momento in cui questa parte viene connessa al circuito completo, esse viene modificata inserendo un opportuno interruttore, connesso alternativamente a 0 e 5V. In questo modo e' possibile azzerare il contatore.

## **Contatore a 4 Bit**

Se avete problemi con il clock "a mano", ad esempio il contatore scatta quando non dovrebbe, provate ad usare il circuito di debouncing

Tensioni di uscita del contatore

|       | $0\ logico\ (mV)$ | $1\ logico\ (V)$ |

|-------|-------------------|------------------|

| $V_0$ | $203 \pm 2$       | $2.98 \pm 0.03$  |

| $V_1$ | $203 \pm 2$       | $2.94 \pm 0.03$  |

| $V_2$ | $215 \pm 2$       | $2.95 \pm 0.03$  |

| $V_3$ | $168 \pm 2$       | $2.93 \pm 0.03$  |

Impostate il numero 0000 agendo sul counter reset e poi il numero 1111 con un clock a ``mano". Verificate con il multimetro il valore delle tensioni delle quattro uscite in corrispondenza dello zero logico e dell'uno logico.

In linea di principio le 4 uscite dovrebbero avere gli stessi valori, ma ...

Questi valori vi serviranno per poi verificare la "scala" del DAC.

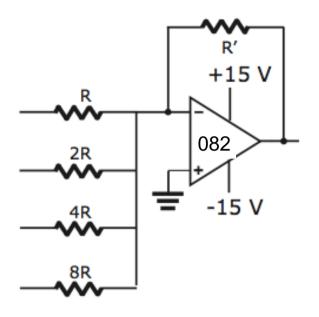

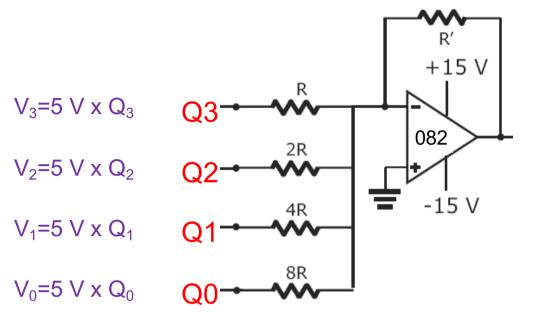

## DAC a 4 bit

Ad esempio

$R \simeq 1 \text{ k}\Omega$

$R' \simeq 1 \div 1.5 \text{ k}\Omega$

Costruire un DAC invertente a pesiera, come in figura. La scelta dei valori di R' ed R deve essere effettuata in modo da avere un'uscita compresa nella massima dinamica d'uscita possibile per l'operazionale, tenendo conto che il circuito e' destinato a ricevere agli ingressi livelli logici TTL (0V/+5V). Inoltre i valori delle resistenze devono essere non troppo piccoli, per evitare eccessivi carichi di corrente. Cercate di selezionare i resistori R, 2R, 4R ed 8R il piu' possibile vicini ai valori nominali, in modo che la scala dei "pesi" sia ragionevolmente vicina a quella ideale.

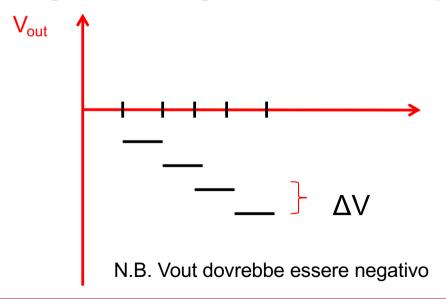

## DAC a 4 bit

$$V_{out} = 5 \times \frac{R'}{8R} \times [Q_0 + 2Q_1 + 4Q_2 + 8Q_3]$$

$V_{out}$

$$V_{out}^{\text{max}} = \left(5 \times \frac{R'}{8R} \times 15\right) \text{ V}$$

N.B. deve essere minore di 15 V, altrimenti l'op-amp taglia l'uscita

$$\left| \frac{R'}{R} < \frac{8}{5} = 1.6 \right|$$

La tensione d'uscita è quantizzata. L'altezza di un gradino vale

$$\Delta V_{out} = 5 \times \frac{R'}{8R} \text{ V}$$

Se si aumenta la sensibilità (cioe' si abbassa il gradino), si riduce la tensione di uscita massima.

#### Verifica del circuito

- 1) Collegate tre ingressi a massa e al quarto mandate un valore continuo di 5 V

- 2) Verificate che la tensione d'uscita corrisponda al valore aspettato V = 5xR'/nR (dove n =1, 2, 4, 8)

## Verifica del DAC e del contatore

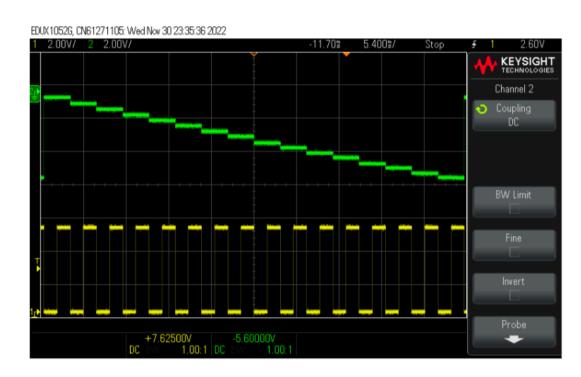

Dopo aver verificato il funzionamento del circuito collegate gli ingressi alle uscite del contatore. Inviando ora un clock a frequenza ragionevolmente elevata utilizzando il generatore di funzione (onda quadrata 0-5V) si potrà visualizzare sull'oscillografo l'andamento temporale della tensione d'uscita. Costruite un grafico della tensione d'uscita in funzione del numero contenuto nel contatore e verificate che la relazione sia approssimativamente lineare, confrontando il risultato con l'andamento atteso sulla base dei valori effettivi delle resistenze utilizzate.

Si deve anche tenere conto del fatto che le 4 uscite del contatore non sono in genere esattamente uguali ai valori nominali dello standard TTL. Tipicamente un "1" logico produce uscite dell'ordine di 3 - 3.5 V; inoltre, in alcuni casi, i valori delle uscite non sono stabili, ma variano lievemente al variare del conteggio. Questo si traduce in un "deterioramento" complessivo della qualità del convertitore, che non inficia tuttavia il suo funzionamento.

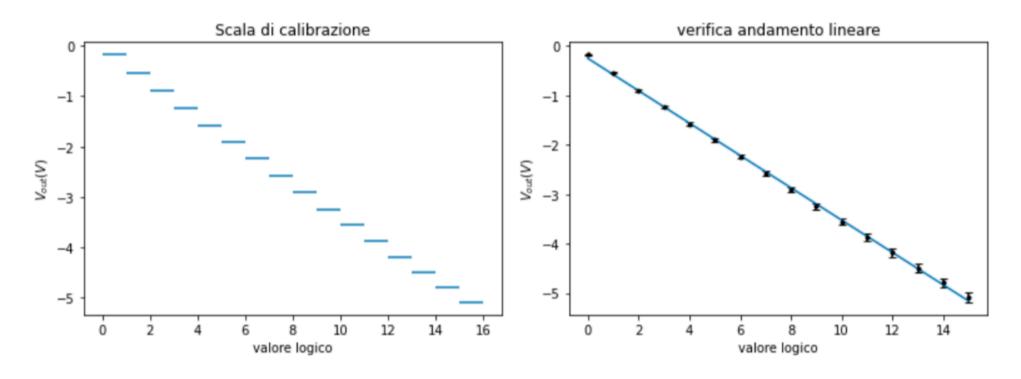

#### Scala di calibrazione

- 1) Impostate con un clock "a mano" i numeri da 0 a 15 e leggete i corrispondenti valori della tensione d'uscita

- 2) Costruite una tabella dove per ciascun numero c'è il valor minimo ed il valore massimo della tensione associata ed il centro dell'intervallo (il valore massimo corrisponde al minimo del numero successivo).

- 3) costruite il grafico a lato

- 4) Verificate la linearita' del grafico

## Verifica del DAC e del contatore

Figura 4: Nella figura è riportato l'andamento temporale dell'uscita del DAC.

Frequenza del clock = 300 Hz

## Calibrazione del DAC

| range (V)          | $\Delta V$ (V) | valor medio (V) | corrispondente logico |

|--------------------|----------------|-----------------|-----------------------|

| $0 \div -0.35$     | 0.35           | -0.18           | 0                     |

| $-0.35 \div -0.73$ | 0.38           | -0.54           | 1                     |

| $-0.73 \div -1.07$ | 0.33           | -0.90           | 2                     |

| $-1.07 \div -1.41$ | 0.34           | -1.24           | 3                     |

| $-1.41 \div -1.74$ | 0.33           | -1.57           | 4                     |

| $-1.74 \div -2.06$ | 0.33           | -1.90           | 5                     |

| $-2.06 \div -2.41$ | 0.35           | -2.24           | 6                     |

| $-2.41 \div -2.72$ | 0.31           | -2.57           | 7                     |

| $-2.72 \div -3.10$ | 0.38           | -2.91           | 8                     |

| $-3.10 \div -3.40$ | 0.30           | -3.25           | 9                     |

| $-3.40 \div -3.72$ | 0.32           | -3.56           | 10                    |

| $-3.72 \div -4.00$ | 0.28           | -3.86           | 11                    |

| $-4.00 \div -4.37$ | 0.37           | -4.19           | 12                    |

| $-4.37 \div -4.63$ | 0.26           | -4.50           | 13                    |

| $-4.63 \div -4.96$ | 0.32           | -4.79           | 14                    |

| $-4.96 \div -5.22$ | 0.26           | -5.09           | 15                    |

Tabella 7: In tabella si riportano il valore massimo, minimo e medio delle tensioni in uscita del DAC relativi a ciascun numero logico e l'altezza di ogni gradino  $\Delta V$ . Si considera un'incertezza strumentale su tutte le misure di tensione dell'1%.

## Verifica della linearità del DAC

Figura 5: Grafico dei valor medi delle tensioni d'uscita del DAC associate ai corrispettivi valori logici e fit di verifica dell'andamento lineare.

## **Comparatore analogico**

Quando  $V_x$  (che è negativo) è minore dell'uscita del DAC (negativa) allora  $V_{out}$  = +15 V (Inizialmente 0 è maggiore di  $-V_x$ , quindi l'uscita è a +15 V), poi mano mano l'uscita del DAC diminuisce (diventa sempre piu' negativa).

Quando l'uscita del DAC diventa minore di  $V_x$ ,  $V_{out}$  commuta e diventa uguale a -15 V. Questo blocca il contatore.

(se il ragionamento non è chiaro, usate i moduli delle tensioni e rimpiazzate minore con maggiore)

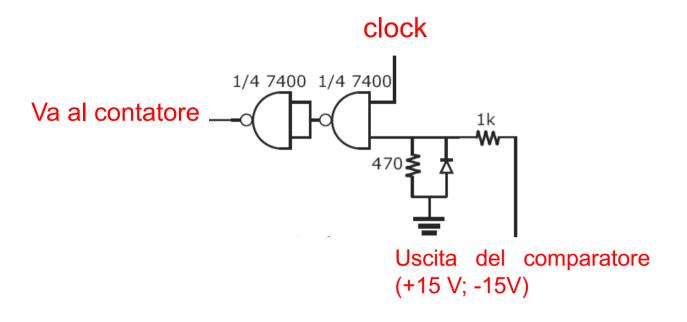

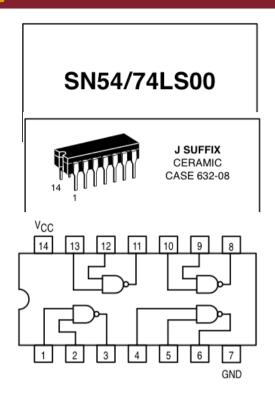

## Adattamento livello TTL e stop del clock

- Il partitore riduce i +15 V a + 5 V.

- Quando l'uscita è -15 V, il diodo va in conduzione ed il livello di potenziale del catodo diventa di 0.6 V (cioè zero logico).

- Quando all'ingresso del NAND c'è 1 logico (+5 V), la sua uscita dipende dal valore del clock presente sull'altro ingresso.

- Quando invece all'ingresso del NAND c'è uno 0 logico, l'uscita del NAND è sempre 1, quindi l'uscita del secondo NAND è sempre 0, qualunque sia il livello logico del clock. In questo modo il contatore viene bloccato e sui led rimane il numero corrispondente al valore di tensione che ha fatto scattare il comparatore.

## Azzeramento del clock

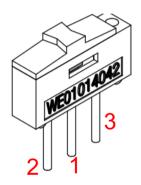

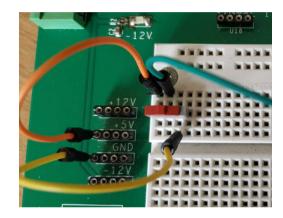

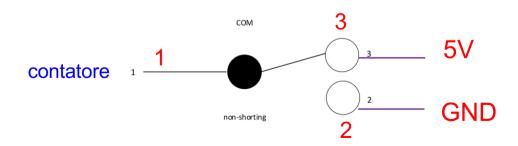

Per fare il "deviatore" non utilizzate un filo volante, ma utilizzare questo switch:

#### Schematic:

I pin 2 e 3 sono simmetrici, potete scambiarli senza problemi.

Il pin centrale deve andare al contatore.

## Circuito completo dell'ADC

1)

3)

4)

# SAPIENZA Fine esercitazione 7