Neuromorphic Computing & Memristors for Particle Physics

Future collider experiments must sift through huge data flux with strict latency and power budgets. Neuromorphic computing and memristive devices open a path to low-latency, energy-efficient, on-detector intelligence, complementing FPGAs/GPUs and helping real-time triggers, reconstruction and calibration.

Motivation (HEP): trigger bandwidth and latency are a hard ceiling; moving smart inference closer to the sensors reduces I/O, lowers power, and can catch subtle physics that hand-crafted cuts might miss.

What is neuromorphic computing?

It’s a computing paradigm inspired by the brain: spiking neural networks (SNNs) process information as streams of discrete events (spikes) in time. Hardware can be digital (event-driven) or analog/mixed-signal, often optimized for latency & energy rather than peak FLOPs.

In particle physics, many neuromorphic ideas are being explored for trigger-level anomaly detection, edge tracking, and fast filtering of streaming data.

Memristors in a nutshell

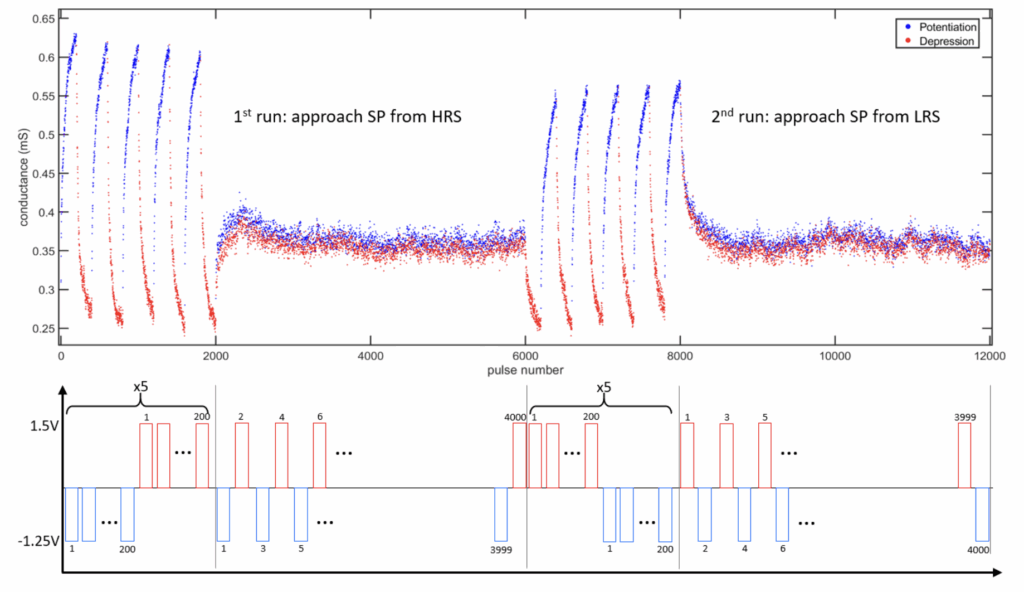

A memristor is a two-terminal device whose resistance remembers past electrical activity. Arrays of memristors arranged in crossbars perform analog vector–matrix multiplies in memory, ideal for neural network layers and scientific linear algebra. This enables O(1) analog matrix operations per column readout (plus peripheral ADC/DAC), drastically reducing data movement.

Why they’re attractive for HEP: non-volatile weights, massive parallelism, very low energy per MAC. Open challenges include device variability, peripheral overheads, endurance, temperature/radiation effects, and algorithm–hardware co-design.

Radiation tolerance: several oxide-based memristive stacks show promising resilience under ionizing radiation, with parameter shifts that can be characterized/compensated; this keeps them in play for on-detector inference.

Applications to particle-physics experiments

We target deployable intelligence for HEP detectors by co-designing algorithms, devices, and mixed-signal electronics. The emphasis is on radiation hardness, on-detector NN inference with deterministic latency, rigorous memristor lab characterization, and ASIC design that fits LHC-style power, timing and reliability budgets.

Use-case focus: trigger-level anomaly/quality flags, hit clustering/region-of-interest preselection, fast solves for calibration/alignment loops — each validated against LHC-like streams and compared to FPGA/GPU baselines for energy, latency, and physics fidelity. See a thesis on Memristors